# Power Modeling for High-Level Power Estimation

Subodh Gupta and Farid N. Najm, Senior Member, IEEE

Abstract-In this paper, we propose a modeling approach that captures the dependence of the power dissipation of a combinational logic circuit on its input/output signal switching statistics. The resulting power macromodel, consisting of a single four-dimensional (4-D) table, can be used to estimate the power consumed in the circuit for any given input/output signal statistics. Given a low-level (typically gate-level) description of the circuit, we describe a characterization process by which such a table model can be automatically built. The four dimensions of our table-based model are the average input signal probability, average input transition density, average spatial correlation coefficient, and average output zero-delay transition density. This approach has been implemented and models have been built for many benchmark circuits. Over a wide range of input signal statistics, we show that this model gives very good accuracy, with an rms error of about 4% and average error of about 6%. Except for one out of about 10 000 cases, the largest error observed was under 20%. If one ignores the glitching activity, then the rms error becomes under 1%, the average error becomes under 5%, and the largest error observed in all cases is under 18%.

Index Terms—Cell-based power estimation, low-power design, power consumption model, static CMOS combinational circuits, switching activity, VLSI.

#### I. Introduction

WITH THE advent of portable and high-density microelectronic devices, the power dissipation of very large scale integrated (VLSI) circuits is becoming a critical concern. Modern microprocessors are hot, and their power consumption can exceed 30 or 50 W. Due to limited battery life, reliability issues, and packaging/cooling costs, power consumption has become a more critical design concern than speed and area in some applications. Hence, to avoid problems associated with excessive power consumption, there is a need for computer-aided design (CAD) tools to help in estimating the power consumption of VLSI designs.

A number of CAD techniques have been proposed for gatelevel power estimation (see [1] for a survey). However, by the time the design has been specified down to the gate level, it may be too late or too expensive to go back and fix high-power problems. Hence, in order to avoid costly redesign steps, power estimation tools are required that can estimate the power consumption at a high level of abstraction, such as when the circuit is

Manuscript received November 25, 1997; revised December 11, 1998. This work was supported by Rockwell, Intel Corporation, and the National Science Foundation under Grants MIP 96-23237 and 97-10235.

Publisher Item Identifier S 1063-8210(00)00758-7.

represented only by the Boolean equations. This will provide the designer with more flexibility to explore design tradeoffs early in the design process, reducing the design cost and time.

In response to this need, a number of high-level power estimation techniques have been proposed (see [2] for a survey). Two styles of techniques have been proposed, which we refer to as top—down and bottom—up. In the top—down techniques [3], [4], a combinational circuit is specified only as a Boolean function, with no information on the circuit structure, number of gates/nodes, etc. Top—down methods would be useful when one is designing a logic block that was not previously designed, so that its internal structural details are unknown.

In contrast, bottom—up methods [5]—[9] are useful when one is reusing a previously designed logic block, so that all the internal structural details of the circuit are known. In this case, one develops a *power macromodel* for this block, which can be used during high-level power estimation (of the overall system in which this block is used), in order to estimate the power dissipation of this block without performing a more expensive gate-level power estimation on it.

The method in [5] uses the power factor approximation technique, which treats all the circuit input bits as digital "white noise" and due to this assumption can give errors of up to 80% in comparison to gate-level tools. Although [6] gives a more accurate result, its main disadvantage is that it treats different modules differently, requiring specialized analytical expressions for the power to be provided by the user. Thus, depending upon the functionality of the module, a different type of macromodel (analytical equation) may have to be used.

The method in [7] characterizes the power dissipation of circuits based on input transitions rather than input statistics. Since the number of possible input transitions for an n-input combinational circuit is  $2^{2n}$ , they present a clustering algorithm to compress the input transitions into clusters of input transitions that have the same power values (approximately). They use heuristics to implement the clustering algorithm, but it is not clear how efficient the method would be on large circuits.

In [8], the authors present a technique to estimate switching activity and power consumption at the register-transfer level (RTL) for data-path and control circuits, in the presence of glitching activity. To construct a power macromodel, they use both analytical equations and lookup tables. The method is quite good and uses nine or more variables in the power macromodel. Our independent work has shown that it is possible to construct a lookup table power macromodel with many fewer variables (four can be enough).

Recently, in [9], the authors presented a macromodel for estimating the cycle-by-cycle power at the RTL. The proposed methodology consists of three steps: module equation form generation and variable selection, variable reduction, and

S. Gupta is with the Electrical and Computer Engineering Department and Coordinated Science Laboratory, University of Illinois at Urbana–Champaign, Urbana, IL 61801 USA (e-mail: sgupta@uivlsi.csl.uiuc.edu).

F. N. Najm is with the Electrical and Computer Engineering Department, University of Toronto, Toronto, Ont., M5S 3G4, Canada (e-mail: f.najm@toronto.edu).

population stratifications. The generated macromodel has 15 variables. They show good accuracy in estimating average and cycle-by-cycle power. The macromodels are dependent on a training vector set, so that the accuracy is compromised if the training set is not similar to the vector set to be applied.

In this paper, we propose a power macromodeling approach that

- takes into account the effect of the circuit input switching activity and does not treat the circuit inputs as white noise;

- 2) takes into account input correlation, both spatial and temporal;

- 3) is based on a single fixed macromodel template, which does not depend on the type of module being analyzed.

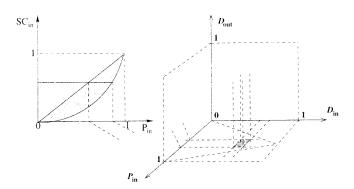

Our model is table-based. Specifically, we construct a four-dimensional (4-D) lookup table, whose axes are the average input signal probability ( $P_{in}$ ), average input transition density ( $D_{in}$ ), average input spatial correlation coefficient (SCin), and average output zero delay transition density  $(D_{\text{out}})$ . For a logic node, the transition density is defined as the average number of logic transitions per unit time [10]. The zero delay transition density refers to the case when the circuit gates are considered to have zero delay, so that only truly required logic transitions (and no hazards or glitches) are observed. From a high-level view, it is reasonable to assume that fast functional simulation will be applied to measure signal switching statistics, so that only the zero delay output density (and not the real delay output density) will be computed. The main advantage of our approach is that all types of circuits are treated in the same way, i.e., we do not use different model equation types for different modules. As a result, the method is very easy to use and requires no user intervention. Indeed, we will present an automatic characterization procedure by which the macromodel can be built for a given circuit. In this paper, we will present an extension of the approach discussed in [11].

This paper is organized as follows. In Section II, we will discuss the macromodeling problem in more detail. In Section III, we will describe the characterization procedure for the models. In Section IV, we will evaluate the accuracy of the macromodels, and in Section V we will give some conclusions.

# II. POWER MACROMODELING

What should a power macromodel look like? Which features are desirable and which are too expensive and infeasible? To begin with, it is clear that a macromodel should be simple to evaluate, otherwise there would be no advantage in using it and one might as well perform the analysis at the gate level. Furthermore, it must apply over the whole range of possible input signal statistics. Last, it should consist of a fixed template, in which certain parameter values can be determined by a well-defined and automatic process of *characterization*, without user intervention. We present a macromodel that has all these properties.

#### A. Power and Input Parameters Relationship

It is instructive to study the relationship between power and input parameters like average probability and average transition

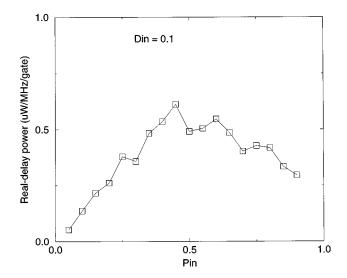

Fig. 1. Plot of total power for c6288, for  $D_{\rm in}=0.1$  and different  $P_{\rm in}$ .

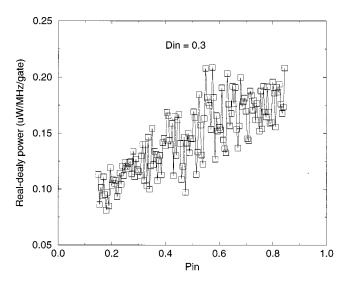

Fig. 2. Plot of total power for c3540, for  $D_{\rm in} = 0.3$  and different  $P_{\rm in}$ .

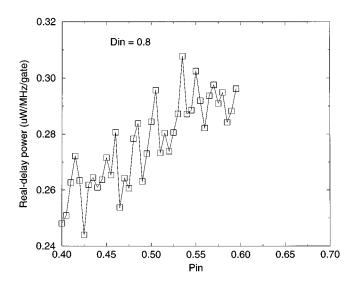

density [see (17) for definitions] of the primary inputs. Simulations were performed for different values of average input probability and average input density to determine the nature of their relationship with power. Fig. 1 shows the plot of real-delay power dissipation for different values of average input probability and average input density for c6288, a combinational benchmark circuit [12]. Figs. 2 and 3 show the same plot for c3540, another combinational benchmark circuit [12]. It can be seen that the relationship is nonlinear and the plots do not have a consistent shape. Similar results were obtained for other circuits. These results preclude, for instance, the use of a simple linear relationship to relate power to the signal statistics, and led us to consider a table-based approach.

## B. Power Macromodeling Assuming Independence

Because the power depends on the circuit input switching activity, it is clear that a power macromodel should take the input activity into account. The question is, however, exactly what information about the inputs should be taken into account and included in the macromodel. When the circuit being modeled is

Fig. 3. Plot of total power for c3540, for  $D_{\rm in}=0.8$  and different  $P_{\rm in}$ .

small (one or a few gates), then a simple modeling strategy is to create a table that gives the power for every possible input vector pair. In this case, there is no loss of accuracy. However, this strategy cannot be applied to large circuits. A circuit with 32 inputs will have 264 possible input vector pairs, which would be prohibitively expensive to store in a table. This leads to a tradeoff between the amount of detail that one includes about the inputs and the accuracy resulting from the model. One possibility is to consider the signal probability  $P(x_i)$  and transition density  $D(x_i)$  at every input node  $x_i$ , and to build a model that depends only on these two variables. Notice that any information about correlations between the input nodes is lost when this is done. Thus, for instance, one could consider building a table which gives the power for every given assignment of input  $P(x_i)$  and  $D(x_i)$  values. Even in this case, however, such a table-based model would be too expensive, because a circuit with 32 inputs would require a 64-dimensional table.

Given the above observations, we have considered what aggregate compact descriptions of the  $P(x_i)$  and  $D(x_i)$  values would be sufficient to model the circuit power. For instance, one could consider building a two-dimensional (2-D) table whose axes would be the average input  $P(x_i)$ , which we will denote by  $P_{\rm in}$ , and the average input  $D(x_i)$ , to be denoted  $D_{\rm in}$ . In this case, two different input assignments of  $P(x_i)$  and  $D(x_i)$  values, which may lead to different power values, may have the same  $P_{\rm in}$  and  $D_{\rm in}$  averages, and the table would predict the same power for both assignments, obviously with some error.

We have studied how big this error can be, as follows. Given a gate-level circuit and for a certain fixed  $P_{\rm in}$  and  $D_{\rm in}$ , we generate a large number (80 or more) of P and D assignments at the circuit inputs that each have averages equal to the specified  $P_{\rm in}$  and  $D_{\rm in}$ . We then perform an accurate power estimation for each assignment using a Monte Carlo gate-level (with full delay model) simulation technique [13]. The average of the resulting power values is a good candidate value to store in the table. For each of the estimated power values, any deviation from this average value is considered to be an "error" relative to this table. The root mean square (rms) and maximum errors for ISCAS85 circuits [12] (see Table I for details of these circuits) are reported

TABLE I

DETAILS OF THE ISCASS5

CIRCUITS

| Circuit | Function          | #inputs | #outputs | #gates |

|---------|-------------------|---------|----------|--------|

| c432    | Interrupt control | 36      | 7        | 160    |

| c880    | ALU               | 60      | 26       | 383    |

| c1908   | Error correction  | 33      | 25       | 880    |

| c2670   | ALU and control   | 233     | 140      | 1193   |

| c3540   | ALU               | 50      | 22       | 1669   |

| c5315   | ALU               | 178     | 123      | 2307   |

| c6288   | Multiplication    | 32      | 32       | 2406   |

| e7552   | ALU               | 207     | 108      | 3512   |

| c499    | Error detection   | 41      | 32       | 202    |

| c1355   | Error detection   | 41      | 32       | 546    |

in Table II, for  $P_{\rm in}=0.4$  and  $D_{\rm in}=0.4$ . A density of 0.4 means that the node makes an average of four transitions in ten consecutive clock cycles. The largest rms error is about 17% and the largest maximum error is -40%.

The power estimator (simulator) used to generate this table uses a scalable-delay timing model that depends on fanout and gate output capacitance. Thus, it captures the glitching power accurately (multiple transitions per cycle due to unequal delay from the inputs to an internal node). The glitching power is hard to account for in a high-level model. This is why such a high rms error is seen for c6288, in which some internal nodes make up to 20 transitions per cycle. The errors improve considerably if the power estimates are based on a zero-delay timing model, in which the glitches are excluded, as shown in Table III. The largest rms error is now 1% and the largest maximum error is 27%.

In any case, with such a high rms error in the general delay case, the total power estimation using Table II is too inaccurate. The simple 2-D table approach is too simplistic. Another parameter is needed by which we can accurately model the variation of the power due to various input P and D assignments. We have

TABLE II

RMS AND MAXIMUM ERROR IN THE 2-D TABLE APPROACH, WHEN

TOTAL POWER IS ESTIMATED

RMS.Error Max.Error  $P_{in}$  $D_{in}$ Circuit 1.61% 34.88% c4320.40.4 0.41.77%40.46%c8800.416.80%c19080.40.41.74%c26700.40.42.43%-31.61% 0.4 35.77%c35400.42.96%20.94%c5315 0.4 1.76% c6288 0.40.4 16.6%-40.04% c75520.4 0.43.37% 19.02%

found that if one more dimension is added to the table, reasonably good accuracy can be obtained. The third axis is the average output transition density over all the circuit output nodes, measured from a zero-delay (functional) simulation of the circuit, and which we will denote by  $D_{\rm out}$ . The stipulation that  $D_{\rm out}$  corresponds to zero-delay is not optional, but rather required for the following reason. We envision that during high-level, say RTL, power estimation, one would perform an initial step of estimating the signal statistics at the visible RTL nodes from a high-level functional simulation. These (zero-delay) statistics would then be applied to the power macromodel in order to estimate the power. Thus, the power model will be given by

$$P_{\text{avg}} = f(P_{\text{in}}, D_{\text{in}}, D_{\text{out}}). \tag{1}$$

In order to study the accuracy in this three-dimensional (3-D) approach, and to perform a direct comparison with Tables II and III, we will show the errors in the estimation for the same  $P_{\rm in}=0.4$  and  $D_{\rm in}=0.4$  specifications as before. The value of  $D_{\rm out}$  will naturally be different in different runs. For each circuit, we selected the largest subset of cases that has the same (approximately)  $D_{\rm out}$  value and examined the errors based on the results in that subset. It is clear from Table IV that the errors are much less now, and the rms error in c6288 is now reduced to an acceptable 6%. For comparison with Table III, the errors in the zero-delay power are given in Table V. The rms error is now below 0.77%, and the maximum error is under about 12%.

TABLE III

RMS AND MAXIMUM ERROR IN THE 2-D TABLE APPROACH, WHEN

ZERO-DELAY POWER IS ESTIMATED

| Circuit | $P_{in}$ | $D_{in}$ | RMS.Error | Max.Error |

|---------|----------|----------|-----------|-----------|

| c432    | 0.4      | 0.4      | 0.59%     | 16.02%    |

| c880    | 0.4      | 0.4      | 0.85%     | 27.5%     |

| c1908   | 0.4      | 0.4      | 0.46%     | -7.28%    |

| c2670   | 0.4      | 0.4      | 0.92%     | -18.82%   |

| c3540   | 0.4      | 0.4      | 0.83%     | -19.07%   |

| c5315   | 0.4      | 0.4      | 0.47%     | 10.88%    |

| c6288   | 0.4      | 0.4      | 0.72%     | -16.82%   |

| c7552   | 0.4      | 0.4      | 1.01%     | -15.54%   |

## C. Power Macromodeling for Correlated Inputs

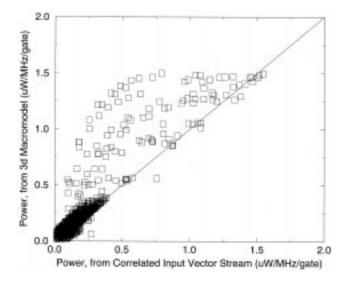

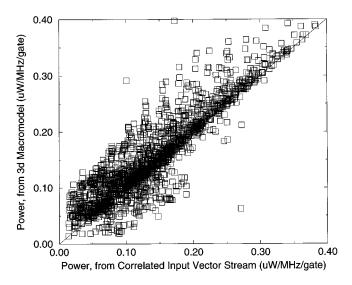

In the previous section we assumed that the primary inputs are independent, but in practice the primary inputs can be correlated. For example, the primary inputs could be the output of another circuit block, which can be very highly correlated. Fig. 4 compares the correlated and 3-D table-based power values for all ISCAS-85 circuits, over a wide range of  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $D_{\rm out}$  values. An enlarged view of the lower section of Fig. 4 is shown in Fig. 5. It can be seen from the figures that the 3-D table-based macromodel gives erroneous estimate of the power when primary inputs are correlated. Table VI gives the rms, average, and maximum error, when the inputs are correlated and the total power is estimated using the 3-D table-based macromodel, over a wide range of  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $D_{\rm out}$  values. It can be seen from the table that the error is quite high. This led us to consider other parameters to be included in the macromodel.

The primary inputs can be either temporally or spatially correlated. A signal x is said to be *temporally correlated* if an event (occurrence of certain logic state) at a given time is correlated to an event at some past time and is said to be *spatially correlated* to another signal y if their events are correlated.

1) Temporal Correlation: In the case of temporal correlation, we will consider only correlations across one clock edge. For temporally correlated primary inputs, define  $TC_i$  for the ith input, as

$$TC_i = \mathcal{P}\{x_i^t \wedge x_i^{t-1} = 1\} \tag{2}$$

TABLE IV

RMS AND MAXIMUM ERROR IN THE 3-D TABLE APPROACH, WHEN

TOTAL POWER IS ESTIMATED

RMS.Error | Max.Error  $D_{in}$  $D_{out}$ Circuit 0.97%16.48%c4320.40.44c8800.40.40.32 1.58%27.87%c19080.40.4 0.44 1.18%12.71%-18.82% 0.40.37 1.78%c26700.41.94% -20.33% 0.40.44c35400.40.421.76%17.16%c53150.40.40.40.446.05%-33.54%c62880.42.97%-15.67%c75520.40.40.42

where

t-1 and t are consecutive clock cycles;

$\mathcal{P}\{\cdot\}$  denotes probability.

Temporal correlation coefficient  $(\gamma_i)$  for the ith input is defined as [14]

$$\gamma_i = \frac{P\{x_i^t \land x_i^{t-1} = 1\} - P(x_i)^2}{P(x_i)(1 - P(x_i))}.$$

(3)

In (3),  $P(x_i)$  is the probability at an input node  $x_i$ , which is known, as individual input probabilities are required to determine  $P_{\rm in}$  for the 3-D table-based power macromodel and the only quantity that is unknown is  $\mathcal{P}\{x_i^t \wedge x_i^{t-1} = 1\}$ . Therefore,  $\gamma_i$  can be estimated accurately, if we can determine  $TC_i$ . But, we will show now that  $TC_i$  can be uniquely determined from the knowledge of  $P(x_i)$  and  $D(x_i)$ .

Proposition 1—For Any Primary Input Node:

$$TC_i = P(x_i) - \frac{D(x_i)}{2} \tag{4}$$

where

$TC_i$  temporal correlation;

$P(x_i)$  signal probability;

$D(x_i)$  transition density.

TABLE V

RMS AND MAXIMUM ERROR IN THE 3-D TABLE APPROACH, WHEN

ZERO-DELAY POWER IS ESTIMATED

| Circuit | $P_{in}$ | $D_{in}$ | $D_{out}$ | RMS.Error | Max.Error |

|---------|----------|----------|-----------|-----------|-----------|

| c432    | 0.4      | 0.4      | 0.44      | 0.33%     | 4.90%     |

| c880    | 0.4      | 0.4      | 0.32      | 0.55%     | 9.87%     |

| c1908   | 0.4      | 0.4      | 0.44      | 0.19%     | -3.23%    |

| c2670   | 0.4      | 0.4      | 0.37      | 0.65%     | -9.70%    |

| c3540   | 0.4      | 0.4      | 0.44      | 0.47%     | -12.37%   |

| c5315   | 0.4      | 0.4      | 0.42      | 0.45%     | 6.32%     |

| c6288   | 0.4      | 0.4      | 0.44      | 0.45%     | -10.18%   |

| e7552   | 0.4      | 0.4      | 0.42      | 0.77%     | -8.82%    |

Fig. 4. Power comparison between correlated input vector stream and 3-D macromodel, when total power is estimated.

*Proof:* Let us denote the probability of a low-to-high transition by  $P_{\rm lh}$  and the probability of a high-to-low transition by  $P_{\rm hl}$ . Since a low-to-high transition is eventually followed by a high-to-low transition, then

$$P_{\rm lh} = P_{\rm hl}. \tag{5}$$

Fig. 5. Power comparison between correlated input vector stream and 3-D macromodel, when total power is estimated.

The transition density can be expressed as

$$D(x_i) = P_{lh} + P_{hl} = 2P_{lh} = 2[P(x_i) - TC_i]$$

(6)

$$\Rightarrow TC_i = P(x_i) - \frac{D(x_i)}{2}. (7)$$

Hence, proved.

Therefore, temporal correlation at the primary inputs is taken care of by  $P(x_i)$  and  $D(x_i)$ , and we do not need an additional parameter to represent it.

2) Spatial Correlation: We will consider only pairwise correlations. We define  $SC_{ij}$ , the spatial correlation between the ith and jth inputs, as

$$SC_{ij} = \mathcal{P}\{x_i \land x_j = 1\}$$

(8)

i.e., the probability of both inputs' being high simultaneously.

The reason for considering  $SC_{ij}$  as the measure of spatial correlation coefficient follows from the definition of correlation coefficient [14]

$$\rho_{ij} = \frac{P\{x_i \land x_j = 1\} - P(x_i)P(x_j)}{\sqrt{P(x_i)P(x_j)(1 - P(x_i))(1 - P(x_j))}}.$$

(9)

From the definition given in (8), it is clear that  $SC_{ij}$  is sufficient to capture  $\rho_{ij}$ .

As the number of primary inputs increases, the number of  $SC_{ij}$  parameters will increase quadratically. We have found empirically that if we consider  $SC_{in}$  (average spatial correlation coefficient, i.e., average of all  $SC_{ij}$  terms), as the fourth parameter in the power macromodel, sufficient accuracy can be obtained for estimating the power of highly correlated primary inputs. Thus, our table-based power macromodel in presence of the fourth parameter looks as follows:

$$P_{\text{avg}} = f(P_{\text{in}}, D_{\text{in}}, SC_{\text{in}}, D_{\text{out}}). \tag{10}$$

TABLE VI RMS, AVERAGE, AND MAXIMUM ERROR WHEN TOTAL POWER OF CORRELATED INPUT VECTOR STREAM IS ESTIMATED USING 3-D MACROMODEL

| Circuit | RMS.Error | Average Error | Max.Error |

|---------|-----------|---------------|-----------|

| c432    | 3.84%     | 35.5%         | 122.16%   |

| c880    | 2.00%     | 16.26%        | 73.9%     |

| c1908   | 3.73%     | 25.75%        | 114.78%   |

| c2670   | 4.46%     | 27.08%        | 116.44%   |

| c3540   | 2.936%    | 20.59%        | 120.01%   |

| c5315   | 3.72%     | 21.72%        | 121.75%   |

| c6288   | 41.4%     | 90.17%        | 226.64%   |

| e7552   | 4.56%     | 28.73%        | 124.34%   |

| c499    | 3.36%     | 43.15%        | 160.79%   |

| c1355   | 2.846%    | 29.66%        | 134.71%   |

# III. CHARACTERIZATION

We assume that the combinational circuit is embedded in a larger sequential circuit, so that its input nodes are the outputs of latches or flip-flops and that they make at most one transition per clock cycle. We assume that the sequential design is a single clock system and ignore clock skew, so that the combinational circuit inputs  $x_1, x_2, \ldots, x_n$  switch only at time 0.

At this point it is helpful to recall some definitions. The signal probability  $P(x_i)$  at an input node  $x_i$  is defined as the average fraction of clock cycles in which the final value of  $x_i$  is a logic high. The transition density  $D(x_i)$  at an input node  $x_i$  is defined as the average fraction of cycles in which the node makes a logic transition (its final value is different from its initial value). For brevity, in this section we will write  $P_i$  and  $D_i$  to represent  $P(x_i)$  and  $D(x_i)$ . Both  $P_i$  and  $D_i$  are real numbers between zero and one.

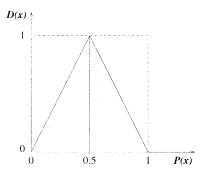

Because the input signals  $x_i$  make at most a single transition per cycle, there is a special relationship between probability and density, given by

$$\frac{D_i}{2} \le P_i \le 1 - \frac{D_i}{2}.\tag{11}$$

Fig. 6. Relationship between density and probability for discrete-time signals.

The derivation of this property is rather simple, as follows. Let  $\mu_1$  ( $\mu_0$ ) be the average number of consecutive clock cycles that an input node remains high (low). Through a minor extension of the results in [10] to the case of discrete time signals, P(x) and D(x) at input node x are given by

$$P(x) = \frac{\mu_1}{\mu_0 + \mu_1} \tag{12}$$

$$D(x) = \frac{2}{\mu_0 + \mu_1} \tag{13}$$

from which it follows that

$$\mu_1 = \frac{2P(x)}{D(x)} \tag{14}$$

$$\mu_0 = \frac{2(1 - P(x))}{D(x)}. (15)$$

Since  $\mu_1 \ge 1$  and  $\mu_0 \ge 1$ , (14) and (15) lead to the required result (11).

One can rewrite (11) as

$$D_i < 1 - 2|P_i - 0.5| \tag{16}$$

so that for a given P(x), D(x) is restricted to the shaded region shown in Fig. 6.

We also recall the definitions of the average input probability, denoted  $P_{\rm in}$ , and average input density, denoted  $D_{\rm in}$ , as follows:

$$P_{\rm in} = \frac{1}{n} \sum_{i=1}^{n} P_i$$

$D_{\rm in} = \frac{1}{n} \sum_{i=1}^{n} D_i$  (17)

where n is the number of input nodes. It is clear from (11) that similar bounds hold for  $P_{\rm in}$  and  $D_{\rm in}$

$$\frac{D_{\rm in}}{2} \le P_{\rm in} \le 1 - \frac{D_{\rm in}}{2}$$

(18)

from which we also have

$$D_{\rm in} \le 1 - 2|P_{\rm in} - 0.5|.$$

(19)

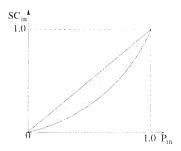

Similarly, we can derive a special relationship between  $SC_{\rm in}$  and  $P_{\rm in}$ , i.e., given  $P_{\rm in}$ , we can find lower and upper bounds for  $SC_{\rm in}$ . Because  $SC_{\rm in}$  is a probability, it can take values only between zero and one. Before describing the bounds, we first recall the definition of  $SC_{\rm in}$

$$SC_{\text{in}} = \frac{2}{n(n-1)} \sum_{i=1}^{n} \sum_{j=i+1}^{n} \mathcal{P}\{x_i = 1, x_j = 1\}$$

(20)

where n is the number of primary inputs.

Let us consider that we have to generate a block of N consecutive input vectors, with each vector consisting of 1's and 0's, and let us denote the kth vector by  $V_k$ .  $SC_{\rm in}$  can be written in terms of the input vectors as

$$SC_{\text{in}} = \lim_{N \to \infty} SC_{\text{in}}^{N} \tag{21}$$

where

$$SC_{\mathbf{in}}^{N} = \frac{1}{N} \sum_{k=1}^{N} \frac{2}{n(n-1)} \sum_{i=1}^{n} \sum_{j=i+1}^{n} x_{i,k} x_{j,k}$$

$$= \frac{2}{n(n-1)N} \sum_{k=1}^{N} \sum_{i=1}^{n} \sum_{j=i+1}^{n} x_{i,k} x_{j,k}$$

(22)

and where  $x_{i,k}$  is the *i*th bit in the *k*th vector. Notice that  $\sum_{i=1}^{n} \sum_{j=i+1}^{n} x_{i,k} x_{j,k} = \text{number of bit pairs, in } k\text{th vector,}$  that are (1,1). Therefore

$$\sum_{i=1}^{n} \sum_{j=i+1}^{n} x_{i,k} x_{j,k} = \frac{n_1(k)(n_1(k)-1)}{2}$$

(23)

where  $n_1(k)$  = number of 1's in  $V_k$ .

By substituting (23) into (22), we get

$$SC_{\text{in}}^{N} = \frac{2}{Nn(n-1)} \sum_{k=1}^{N} \frac{n_1(k)(n_1(k)-1)}{2}.$$

(24)

At this point, it will be helpful to define  $P_{\rm in}^N$ . For a block of N vectors,  $P_{\rm in}$  can be written as

$$P_{\rm in} = \lim_{N \to \infty} P_{\rm in}^N \tag{25}$$

where

$$P_{\rm in}^N = \frac{1}{N} \sum_{k=1}^N \frac{n_1(k)}{n}.$$

(26)

Notice that for large N

$$\frac{1}{N} \sum_{k=1}^{N} n_1(k) \approx n P_{\text{in}}.$$

(27)

It can be shown from (24) and (26) that, if we allow  $n_1(k)$  to take real noninteger values, then the minimum value of  $SC_{\rm in}^N$  occurs when, for all k (see Appendix A for proof)

$$n_1(k) = nP_{\rm in}^N. \tag{28}$$

Therefore, a lower bound on  $SC_{\mathbf{in}}^N$  is given by

$$SC_{\rm in}^N \ge \frac{nP_{\rm in}^N(nP_{\rm in}^N - 1)}{n(n-1)}.$$

(29)

For large values of N, this leads to

$$SC_{\rm in} \ge \frac{nP_{\rm in}^2 - P_{\rm in}}{(n-1)}.$$

(30)

To compute an upper bound on  $SC_{\mathrm{in}}^N$ , we start with the observation that the maximum value of  $SC_{\mathrm{in}}^N$  in (24) will occur when as many  $n_1(k)$ 's as possible are set to their maximum value n, because of the quadratic term. Since not all  $n_1(k)$ 's can be set to n due to (26), the largest  $SC_{\mathrm{in}}^N$  is achieved by having m < N vectors have  $n_1(k) = n$  1's, one vector contain the remaining r < n 1's, and the remaining vectors contain all 0's. In other words, m is the largest integer for which  $mn + r = \sum_{k=1}^{N} n_1(k) = NnP_{\mathrm{in}}^N$ , where 0 < r < n is an

Fig. 7. Relationship between probability and spatial correlation for discrete-time signals.

integer. With this,  $m=\lfloor NP_{\rm in}^N\rfloor$ , and the largest possible value of  $SC_{\rm in}^N$  is given by

$$SC_{\text{in}}^{N} \le \frac{mn(n-1) + r(r-1)}{Nn(n-1)} = \frac{m}{N} + \frac{r(r-1)}{Nn(n-1)}.$$

(31)

From this, it follows that

$$SC_{\text{in}} = \lim_{N \to \infty} SC_{\text{in}}^N \le P_{\text{in}}$$

(32)

due to the fact that  $m/N=P_{\rm in}^N-(r/Nn)$  so that  $\lim_{N\to\infty}m/N=P_{\rm in}.$

Combining the lower and upper bounds gives

$$\frac{nP_{\rm in}^2 - P_{\rm in}}{(n-1)} \le SC_{\rm in} \le P_{\rm in}.$$

(33)

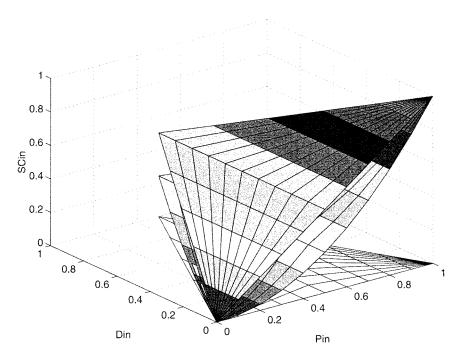

The shaded region in Fig. 7 shows the feasible region for  $P_{\rm in}$  and  $SC_{\rm in}$ . Shown in Fig. 8 is the 3-D plot showing the relationship between  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$ . The two shaded surfaces are the lower and upper bounds for  $SC_{\rm in}$  for different values of  $P_{\rm in}$  and  $D_{\rm in}$ . It is evident from the figure that  $D_{\rm in}$  does not have any effect on  $SC_{\rm in}$ . The surface in the  $(P_{\rm in}\ D_{\rm in})$  plane shows the relationship between  $P_{\rm in}$  and  $D_{\rm in}$  as given by (18).

Thus, the 4-D table with axes  $P_{\rm in}$ ,  $D_{\rm in}$ ,  $SC_{\rm in}$ , and  $D_{\rm out}$  will not be completely full, and the choices of  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$  during characterization will have to satisfy the above constraints (18) and (33). We subdivide the probability, density, and spatial correlation axes between zero and one into intervals of size 0.1, so that we form a  $10 \times 10 \times 10$  grid in the  $(P_{\rm in}, D_{\rm in}, SC_{\rm in})$  plane. This choice is rather an arbitrary one, which we have found works well. Only a fraction of these points are valid, namely, those that fall inside the shaded regions in Figs. 7 and 8. Each valid grid point will correspond to a column of cells in the table along the  $D_{\rm out}$  axis as shown in Fig. 9.

For each valid grid point in the  $(P_{\rm in}, D_{\rm in}, SC_{\rm in})$  space, we generate blocks of input vectors such that the average probability, density, and spatial correlation at the primary inputs are equal to  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$ , respectively. Using these vectors, the circuit power is computed using Monte Carlo power estimation [13], and the value of  $D_{\rm out}$  is computed as the average of the individual (zero-delay) density values at the circuit outputs, also found during the Monte Carlo analysis. The value of  $D_{\rm out}$  is rounded to the nearest grid point on the  $D_{\rm out}$  axis, and the power value obtained is associated with the resulting cell location  $(P_{\rm in}, D_{\rm in}, SC_{\rm in}, D_{\rm out})$  in the table. Eventually, a number

of power values may be associated with a single cell in the table. At the end of the characterization, every cell is filled with the average of the power values associated with it. Some cells may have no power values associated with them, in which case their contents are left at zero. When it comes time to use the table, interpolation and extrapolation can be used to find the power for a  $(P_{\rm in}, D_{\rm in}, SC_{\rm in}, D_{\rm out})$  combination, which does not exist in the table. In the next section, we will show a number of results that demonstrate the accuracy of this approach over a wide range of input statistics, in which interpolation and extrapolation were used whenever required.

The above characterization process is straightforward, except for the generation of the block of input vectors at the primary inputs such that the average values of probability, density, and spatial correlation are equal to  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$ , respectively.

Mathematically, the problem can be stated as to generate a block of N input vectors (as shown in Fig. 10) such that they satisfy the following requirements:

$$P_{\text{in}}^{N} \approx P_{\text{in}}$$

$$D_{\text{in}}^{N} \approx D_{\text{in}}$$

$$SC_{\text{in}}^{N} \approx SC_{\text{in}}$$

(34)

where  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$  are the required average signal probability, average transition density, and average spatial correlation coefficient, respectively, at the primary inputs, which satisfy (18) and (33). Similarly,  $P_{\rm in}^N$ ,  $D_{\rm in}^N$ , and  $SC_{\rm in}^N$  are the averages obtained from the generated input vectors.

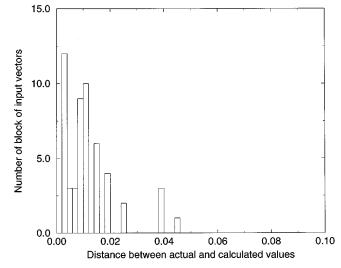

We have developed a heuristic technique to generate blocks of input vectors satisfying (34). Fig. 11 shows a histogram of the Euclidean distance between  $(P_{\rm in}, D_{\rm in}, SC_{\rm in})$  and  $(P_{\rm in}^N, D_{\rm in}^N, SC_{\rm in}^N)$ , for blocks of input vector of size N=100, over a wide range of  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$  values. It is clear from the figure that for most cases the distance is near zero, and that the maximum error is under 5%, thus demonstrating the accuracy of this technique. For more details on this, refer to [15].

Table VII gives the execution times for the ISCAS-85 circuits, under the column named "Time," for building the lookuptable-based macromodel. The execution times are on a Sun UltraSPARC 1 with 64 MB of RAM. It can be seen from the table that the largest execution times are required for c7552 and c6288, respectively. This is due to the fact that it is very time consuming to compute the power dissipation for these circuits. The number of iterations (power estimation runs) required to build the macromodel is the same for all the circuits, including c7552 and c6288. If one uses a more efficient power estimator, the overall time to build the macromodel would be reduced. In any case, it should be kept in mind that the time required to build the macromodel is a one-time up-front cost.

#### IV. MODEL ACCURACY EVALUATION

In this section, we report the results of the 4-D power macromodeling approach on the ISCAS-85 circuits. We have implemented this approach and built the power macromodels (4-D lookup tables) for a number of combinational circuits. In order to study the accuracy over a wide range of signal statistics, we

Fig. 8. Relationship among probability, density, and spatial correlation for discrete-time signals.

Fig. 9. Four-dimensional power macromodel.

|                   | $X_1$ | $X_2$ | X <sub>3.</sub> |       | $X_{n-1}$ | $X_n$ |

|-------------------|-------|-------|-----------------|-------|-----------|-------|

| $\mathbf{V}_1$    | 1     | 1     | 0               | • • • | 0         | 1     |

| $V_2$ $V_3$       | 0     | 0     | 1               |       | 0         | 1     |

| $V_3$             | 1     | 0     | 1               |       | 1         | 1     |

|                   |       |       |                 |       |           |       |

|                   |       |       |                 |       |           |       |

|                   |       |       |                 | •     |           |       |

|                   |       |       |                 | •     |           |       |

|                   |       |       |                 | •     |           |       |

|                   |       |       |                 |       |           |       |

|                   |       |       |                 |       |           |       |

| $V_{N-1}$         | 0     | 0     | 1               |       | 1         | 0     |

| $V_{N-1}$ $V_{N}$ | 1     | 1     | 1               |       | 0         | 0     |

Fig. 10. A block of N input vectors.

randomly generated blocks of input vectors at the circuit inputs while covering a wide range of  $P_{\rm in}$ ,  $D_{\rm in}$ , and  $SC_{\rm in}$  values that satisfy (18) and (33). Approximately 1000 such valid blocks of

Fig. 11. Distance distribution between  $(P_{\rm in},D_{\rm in},SC_{\rm in})$  and  $(P_{\rm in}^N,SC_{\rm in}^N)$ .

input vectors were generated this way for every ISCAS-85 circuits, for which the power was estimated from gate-level Monte Carlo simulation; the Monte Carlo simulation also provides accurate estimation of  $D_{\rm out}$ . The power values predicted by the lookup table were compared to those from simulation, and the rms, absolute average and maximum errors were computed.

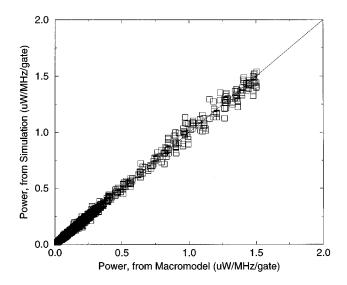

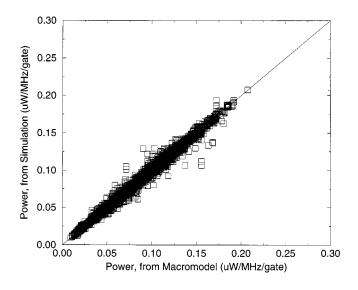

The results are summarized in Table VII for the case when total power is estimated. It is seen that the rms error is very good, under about 5%. The largest maximum error is at 22.56% for c432, because the estimated power value is very small and a slight difference in power value causes a lot of error. The average error in all cases is less than 6%, which shows the accuracy of our macromodeling approach. The combined scatter plot of all ISCAS-85 circuits showing the accuracy of this approach is shown in Fig. 12. An enlarged view of the lower section of this

| TABLE                              | VII                           |

|------------------------------------|-------------------------------|

| ACCURACY OF THE 4-D LOOKUP TABLES. | WHEN TOTAL POWER IS ESTIMATED |

| Circuit | RMS.Error | Average Error | Max.Error | Time     |

|---------|-----------|---------------|-----------|----------|

| c432    | 0.868%    | 5.56%         | 22.56%    | 11.75hrs |

| c880    | 0.647%    | 3.73%         | 14.64%    | 6.24hrs  |

| c1908   | 0.729%    | 3.85%         | 16.89%    | 4.59hrs  |

| c2670   | 0.738%    | 3.08%         | 11.52%    | 14.23hrs |

| c3540   | 0.802%    | 3.61%         | 16.53%    | 21.32hrs |

| c5315   | 0.612%    | 2.48%         | -14.58%   | 16.21hrs |

| c6288   | 4.14%     | 3.75%         | 18.23%    | 34.4hrs  |

| e7552   | 0.847%    | 3.03%         | -16.58%   | 58.4hrs  |

| c499    | 0.497%    | 4.05%         | 16.4%     | 2.3hrs   |

| c1355   | 0.5167%   | 4.19%         | 15.6%     | 2.09hrs  |

plot is given in Fig. 13. Both these plots report normalized power values, so that the results for all the circuits can be examined on the same plot.

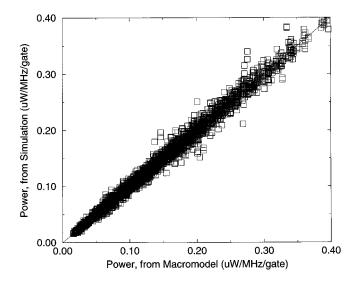

For completeness, the accuracy of the macromodels when zero-delay power is estimated is shown in Table VIII and in the scatter plot in Fig. 14. Over a wide range of signal statistics, the rms error is below 0.60%, the average error is under 5%, and the maximum error is under 18%. The scatter plot also shows excellent agreement.

#### V. CONCLUSION

Since gate-level power estimation can be time-consuming and because power estimation from a high level of abstraction is desirable so as to reduce design time and cost, we have proposed a power macromodeling approach for combinational circuits with synchronous inputs. Our macromodel consists of a 4-D lookup table with axes for average input signal probability, average input transition density, average input spatial correlation coefficient, and average output (zero-delay) transition density. A novel and significant aspect of this approach is that

Fig. 12. Agreement between the 4-D table and accurate power estimation, when total power is estimated.

Fig. 13. Agreement between the 4-D table and accurate power estimation, when total power is estimated, enlarged view.

we use the same model template for all types of combinational circuits, and no specialized analytical expressions are required. Another important fact is that this model works for all possible signal switching statistics.

We have shown why it is advantageous to use a 4-D table and described an automatic procedure for building the 4-D macromodel, without the need for user intervention. Once the model for a combinational block has been built, it can be used to estimate power during high-level power estimation, based on signal statistics that are computed from a high-level functional simulation. Over a wide range of input/output signal statistics, we have shown that this model gives very good accuracy, with an rms error of about 4%. Except for one out of about 10 000 cases, the largest error observed was under 20%. The average error was under 6%. If one ignores the glitching activity, then the rms error becomes under 0.60%, the average error under 5%, and the largest maximum error under 18%.

TABLE VIII

ACCURACY OF THE 4-D LOOKUP TABLES, WHEN ZERO-DELAY POWER

IS ESTIMATED

| Circuit | RMS.Error | Average Error | Max.Error |

|---------|-----------|---------------|-----------|

| c432    | 0.428%    | 4.409%        | 17.35%    |

| c880    | 0.519%    | 3.62%         | 13.97%    |

| c1908   | 0.461%    | 3.73%         | 15.69%    |

| c2670   | 0.307%    | 2.18%         | 10.16%    |

| c3540   | 0.413%    | 3.22%         | 15.55%    |

| c5315   | 0.29%     | 2.08%         | -12.20%   |

| c6288   | 0.332%    | 2.218%        | 17.37%    |

| c7552   | 0.23%     | 2.65%         | -14.32%   |

| c499    | 0.45%     | 3.95%         | 16.34%    |

| c1355   | 0.383%    | 4.03%         | 15.04%    |

Fig. 14. Agreement between the 4-D table and accurate power estimation, when zero-delay power is estimated.

#### APPENDIX A

We will derive the values of  $n_1(k)$ , for which  $SC_{\rm in}^N$  and hence  $SC_{\rm in}$  takes its minimum value, in support of the result (28). We start by writing (24) as

$$\sum_{k=1}^{N} n_1^2(k) - \sum_{k=1}^{N} n_1(k) = n(n-1)NSC_{\text{in}}^N.$$

(A.1)

From (26), we have

$$\sum_{k=1}^{N} n_1(k) = nNP_{\text{in}}^{N}$$

(A.2)

which is a constant. Therefore, the minimization problem becomes

minimize

$$\sum_{k=1}^{N} n_1^2(k)$$

such that

$$\sum_{k=1}^{N} n_1(k) = nNP_{\rm in}^N. \tag{A.3}$$

Proposition A1: If  $n_1(k)$  are allowed to take real noninteger values, then the minimum value of  $\sum_{k=1}^{N} n_1^2(k)$ , subject to (A.2), occurs when for all k

$$n_1(k) = nP_{\rm in}^N. \tag{A.4}$$

*Proof:* The problem given by (A.3) is a constrained minimization problem. Because it is a convex problem, it can be solved by converting it (by introducing a Lagrangian) into an unconstrained problem [16], leading to

$$\label{eq:minimize} \text{minimize} \quad \sum_{k=1}^{N} n_1^2(k) - \lambda \left( nNP_{\text{in}}^N - \sum_{k=1}^{N} n_1(k) \right) \quad \text{(A.5)}$$

where  $\lambda$  is a constant. Differentiating  $\sum_{k=1}^{N} n_1^2(k) - \lambda(nNP_{\text{in}}^N - \sum_{k=1}^{N} n_1(k))$  with respect to  $n_1(k)$  and setting it equal to zero, we get

$$n_1(k) = -\frac{\lambda}{2}. (A.6)$$

Plugging this value of  $n_1(k)$  into (A.2), we get

$$\lambda = -2nP_{\rm in}^N \tag{A.7}$$

$$\Rightarrow n_1(k) = nP_{\rm in}^N. \tag{A.8}$$

Hence, proved.

#### REFERENCES

- [1] F. Najm, "A survey of power estimation techniques in VLSI circuits," *IEEE Trans. VLSI Syst.*, vol. 2, pp. 446–455, Dec. 1994.

- [2] P. Landman, "High-level power estimation," in *Proc. Int. Symp. Low Power Electronics and Design*, Monterey, CA, Aug. 12–14, 1996, pp. 29–35.

- [3] M. Nemani and F. Najm, "Towards a high-level power estimation capability," *IEEE Trans. Computer-Aided Design*, vol. 15, pp. 588–598, June 1996.

- [4] D. Marculescu, R. Marculescu, and M. Pedram, "Information theoretic measures of energy consumption at register transfer level," in *Proc.* ACM/IEEE Int. Symp. Low Power Design, Apr. 1995, pp. 87–92.

- [5] S. R. Powell and P. M. Chau, "Estimating power dissipation of VLSI signal processing chips: The PFA technique," in *Proc. VLSI Signal Pro*cessing IV, 1990, pp. 250–259.

- [6] P. E. Landman and J. M. Rabaey, "Architectural power analysis: The dual bit type method," *IEEE Trans. VLSI Syst.*, vol. 3, pp. 173–187, June 1995.

- [7] H. Mehta, R. M. Owens, and M. J. Irwin, "Energy characterization based on clustering," in *Proc. 33rd ACM/IEEE Design Automation Conf.*, June 1996, pp. 702–707.

- [8] A. Raghunathan, S. Dey, and N. K. Jha, "Register-transfer level estimation techniques for switching activity and power consumption," in *Proc. IEEE Int. Conf. Computer-Aided Design*, Nov. 1996, pp. 158–165.

- [9] Q. Qiu, Q. Wu, C.-S. Ding, and M. Pedram, "Cycle-accurate macromodels for RT-level power analysis," in *Proc. Int. Symp. Low Power Electronics and Design*, 1997, pp. 125–130.

- [10] F. Najm, "Transition density: A new measure of activity in digital circuits," *IEEE Trans. Computer-Aided Design*, vol. 12, pp. 310–323, Feb. 1993.

- [11] S. Gupta and F. Najm, "Power macromodeling for high level power estimation," in *Proc. 34th ACM/IEEE Design Automation Conf.*, June 1997, pp. 365–370.

- [12] F. Brglez and H. Fujiwara, "A neutral netlist of 10 combinational benchmark circuits and a target translator in Fortran," in *Proc. IEEE Int. Symp. Circuits and Systems*, June 1985, pp. 695–698.

- [13] M. Xakellis and F. Najm, "Statistical estimation of the switching activity in digital circuits," in *Proc. 31st ACM/IEEE Design Automation Conf.*, June 1994, pp. 728–733.

- [14] A. Papoulis, *Probability, Random Variables, and Stochastic Processes*, 3rd ed. New York: McGraw-Hill, 1991.

- [15] S. Gupta and F. Najm, "Power macromodeling for high level power estimation," Univ. Illinois, Rep. UILU-ENG-97-2229, Sept. 1997.

[16] D. G. Luenberger, Linear and Nonlinear Programming, 2nd ed. Reading, MA: Addison-Wesley, 1984.

Subodh Gupta was born in India on May 28, 1974. He received the B.Tech. (Hons.) degree from the Indian Institute of Technology, Kharagpur, in 1995 and the M.S. degree from the University of Illinois at Urbana–Champaign in 1997, both in electrical engineering. He is currently working towards the Ph.D. degree in electrical engineering at the University of Illinois at Urbana–Champaign. His Ph.D. research is focused on high-level power estimation and modeling.

During the summer of 1996, he was at Intel Corporation, Santa Clara, CA. His research interests include computer-aided design of VLSI circuits for power estimation, low-power design methodologies, and high-level power estimation.

**Farid N. Najm** (S'85–M'89–SM'96) received the Ph.D. degree in electrical and computer engineering (ECE) from the University of Illinois at Urbana–Champaign (UIUC) in 1989.

He was with Texas Instruments, Inc., before rejoining the ECE Department, UIUC, in 1992 as Assistant Professor. He was promoted to Tenured Associate Professor in 1997. Since 1999, he has been with the ECE Department at the University of Toronto, Toronto, Ont., Canada. He is an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE

SCALE INTEGRATION SYSTEMS and has served as Column Editor for the IEEE CIRCUITS AND DEVICES MAGAZINE.

Dr. Najm received the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN Best Paper Award in 1992, the NSF Research Initiation Award in 1993, and the NSF CAREER Award in 1996. He has served as General Chairman for the 1999 International Symposium on Low-Power Electronics and Design (ISLPED-99), as Technical Program Cochairman for ISLPED-98, and as Technical Program Chairman for the 1997 Great Lakes Symposium on VLSI. He has also served on the technical committees of ICCAD, DAC, CICC, and ISLPED.