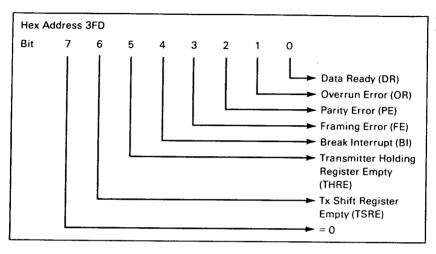

## Line Status Register

This 8-bit register provides status information on the processor concerning the data transfer. The contents of the line status register are indicated and described below:

Line Status Register (LSR)

Bit 0: This bit is the receiver data ready (DR) indicator. Bit 0 is set to a logical 1 whenever a complete incoming character has been received and transferred into the receiver buffer register. Bit 0 may be reset to a logical 0 either by the processor reading the data in the receiver buffer register or by writing a logical 0 into it from the processor.

Bit 1: This bit is the overrun error (OE) indicator. Bit 1 indicates that data in the receiver buffer register was not read by the processor before the next character was transferred into the receiver buffer register, thereby destroying the previous character. The OE indicator is reset whenever the processor reads the contents of the line status register.

Bit 2: This bit is the parity error (PE) indicator. Bit 2 indicates that the received data character does not have the correct even or odd parity, as selected by the even parity-select bit. The PE bit is set to a logical 1 upon detection of a parity error and is reset to a logical 0 whenever the processor reads the contents of the line status register.

- Bit 3: This bit is the framing error (FE) indicator. Bit 3 indicates that the received character did not have a valid stop bit. Bit 3 is set to a logical 1 whenever the stop bit following the last data bit or parity is detected as a zero bit (spacing level).

- Bit 4: This bit is the break interrupt (BI) indicator. Bit 4 is set to a logical 1 whenever the received data input is held in the spacing (logical 0) state for longer than a full word transmission time (that is, the total time of start bit + data bits + parity +stop bits).

Note: Bits 1 through 4 are the error conditions that produce a receiver line status interrupt whenever any of the corresponding conditions are detected.

- Bit 5: This bit is the transmitter holding register empty (THRE) indicator. Bit 5 indicates that the INS8250 is ready to accept a new character for transmission. In addition, this bit causes the INS8250 to issue an interrupt to the processor when the transmit holding register empty interrupt enable is set high. The THRE bit is set to a logical 1 when a character is transferred from the transmitter holding register into the transmitter shift register. The bit is reset to logical 0 concurrently with the loading of the transmitter holding register by the processor.

- Bit 6: This bit is the transmitter shift register empty (TSRE) indicator. Bit 6 is set to a logical 1 whenever the transmitter shift register is idle. It is reset to logical 0 upon a data transfer from the transmitter holding register to the transmitter shift register. Bit 6 is a read-only bit.

- Bit 7: This bit is permanently set to logical 0.

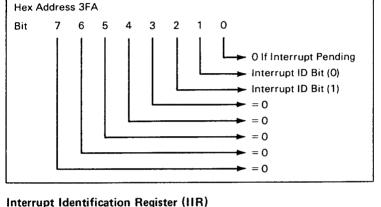

## Interrupt Identification Register

The INS8250 has an on-chip interrupt capability that allows for complete flexibility in interfacing to all the popular microprocessors presently available. In order to provide minimum software overhead during data character transfers, the INS8250 prioritizes interrupts into four levels: receiver line status (priority 1), received data ready (priority 2), transmitter holding register empty (priority 3), and modem status (priority 4).

the type of prioritized interrupt is stored in the interrupt identification register. Refer to the "Interrupt Control Functions" table. The interrupt identification register (IIR), when addressed during chip-select time, freezes the highest priority interrupt pending, and no other interrupts are acknowledged until that particular interrupt is serviced by the processor. The contents

Information indicating that a prioritized interrupt is pending and

of the IIR are indicated and described below.

montabe radication regions (...

polled environment to indicate whether an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logical 1, no interrupt is pending and polling (if used) is continued.

Bit 0: This bit can be used in either a hard-wired prioritized or

Bits 1 and 2: These two bits of the IIR are used to identify the highest priority interrupt pending as indicated in the "Interrupt Control Functions" table.

Bits 3 through 7: These five bits of the IIR are always logical 0.

| Interrupt ID<br>Register |       |       | Interrupt Set and Reset Functions |                                             |                                                                                                       |                                                                                                    |

|--------------------------|-------|-------|-----------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Bit 2                    | Bit 1 | Bit O | Priority<br>Level                 | Interrupt<br>Type                           | Interrupt<br>Source                                                                                   | Interrupt<br>Reset Control                                                                         |

| 0                        | 0     | 1     | -                                 | None                                        | None                                                                                                  | _                                                                                                  |

| 1                        | 1     | 0     | Highest                           | Receiver<br>Line Status                     | Overrun Error<br>or<br>Parity Error<br>or<br>Framing Error<br>or<br>Break Interrupt                   | Reading the<br>Line Status<br>Register                                                             |

| 1                        | 0     | 0     | Second                            | Received<br>Data Available                  | Receiver<br>Data Available                                                                            | Reading the<br>Receiver Buffer<br>Register                                                         |

| 0                        | 1     | 0     | Third                             | Transmitter<br>Holding<br>Register<br>Empty | Transmitter<br>Holding<br>Register<br>Empty                                                           | Reading the IIR Register (if source of interrupt) or Writing into the Transmitter Holding Register |

| 0                        | 0     | 0     | Fourth                            | Modem<br>Status                             | Clear to Send<br>or<br>Data Set Ready<br>or<br>Ring Indicator<br>or<br>Received Line<br>Signal Direct | Reading the<br>Modem Status<br>Register                                                            |