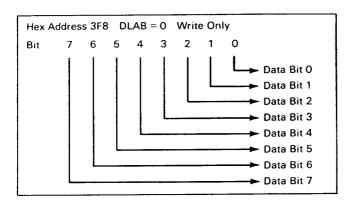

## Transmitter Holding Register

The transmitter holding register contains the character to be serially transmitted and is defined below:

Transmitter Holding Register (THR)

Bit 0 is the least significant bit and is the first bit serially transmitted.

Bit 3: This bit is the delta received line signal detector (DRLSD) indicator. Bit 3 indicates that the  $\overline{RLSD}$  input to the chip has changed state.

Note: Whenever bit 0, 1, 2, or 3 is set to a logical 1, a modem status interrupt is generated.

Bit 4: This bit is the complement of the clear to send  $(\overline{CTS})$  input. If bit 4 (LOOP) of the MCR is set to a logical 1, this is equivalent to RTS in the MCR.

Bit 5: This bit is the complement of the data set ready ( $\overline{DSR}$ ) input. If bit 4 of the MCR is set to a logical 1, this bit is equivalent to DTR in the MCR.

Bit 6: This bit is the complement of the ring indicator  $(\overline{RI})$  input. If bit 4 of the MCR is set to a logical 1, this bit is equivalent to OUT 1 in the MCR.

Bit 7: This bit is the complement of the received line signal detect (RLSD) input. If bit 4 of the MCR is set to a logical 1, this bit is equivalent to OUT 2 of the MCR.

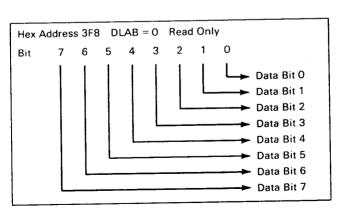

## Receiver Buffer Register

The receiver buffer register contains the received character as defined below:

Receiver Buffer Register (RBR)

Bit 0 is the least significant bit and is the first bit serially received.

1 Adamson 1 24